S5PV210的时钟系统

S5PV210的时钟系统

什么是时钟?SoC为什么需要时钟?

(1)时钟是同步工作系统的同步节拍。

(2)SoC内部有很多器件,譬如CPU、串口、DRAM控制器、GPIO等内部外设,这些东西要彼此协同工作,需要一个同步的时钟系统来指挥。这个就是我们SoC的时钟系统。

时钟一般如何获得

(1)SoC的时钟获得一般有:

- 外部直接输入时钟信号,SoC有个引脚用来输入外部时钟信号,用的很少。

- 外部晶振+内部时钟发生器产生时钟,大部分低频单片机都是这么工作的。

- 外部晶振+内部时钟发生器+内部PLL产生高频时钟+内部分频器分频得到各种频率的时钟,210属于这种。

(2)S5PV210属于第三种。为什么这么设计?

第一问:外什么不用外部高频晶振产生高频信号直接给CPU?

主要是因为芯片外部电路不适宜使用高频率,因为传导辐射比较难控制;高频率的晶振太贵了。

第二问:为什么要内部先高频然后再分频?

主要因为SoC内部有很多部件都需要时钟,而且各自需要的时钟频率不同,没法统一供应。因此设计思路是PLL后先得到一个最高的频率(1GHz、1.2GHz),然后各外设都有自己的分频器再来分频得到自己想要的频率。

时钟和系统性能的关系、超频、稳定性

(1)一般SoC时钟频率都是可以人为编程控制的,频率的高低对系统性能有很大影响。

(2)S5PV210建议工作频率800MHz~1.2GHz,一般我们都设置到1GHz主频。如果你设置到1.2GHz就叫超频。超频的时候系统性能会提升,但是发热也会增大,因此会影响系统稳定性。

时钟和外设编程的关联

(1)每个外设工作都需要一定频率的时钟,这些时钟都是由时钟系统提供的。时钟系统可以编程控制工作模式,因此我们程序员可以为每个外设指定时钟来源、时钟分频系统、从而制定这个外设的工作时钟。

时钟和功耗控制的关系

(1)SoC中各种设备工作时,时钟频率越高其功耗越大,发热越大,越容易不稳定,需要外部的散热条件越苛刻。

(2)SoC内部有很多外设,这些外设不用的时候最好关掉(不关掉会一定程度浪费电),开关外设不是通过开关,而是通过时钟。也就是说我们给某个外设断掉时钟,这个外设就不工作了。

时钟域:MSYS、DSYS、PSYS

(1)因为S5PV210的时钟体系比较复杂,内部外设模块太多,因此把整个内部的时钟划分为3大块,叫做3个域。

(2)MSYS: CPU(Cortex-A8内核)、DRAM控制器(DMC0和DMC1)、IRAM&IROM······

(3)DSYS: 都是和视频显示、编解码等有关的模块

(4)PSYS: 和内部的各种外设时钟有关,譬如串口、SD接口、I2C、AC97、USB等。

(5)为什么内部要分为3个域,怎么划分的?因为210内部的这些模块彼此工作时钟速率差异太大了,所以有必要把高速的放一起,相对低速的放一起。

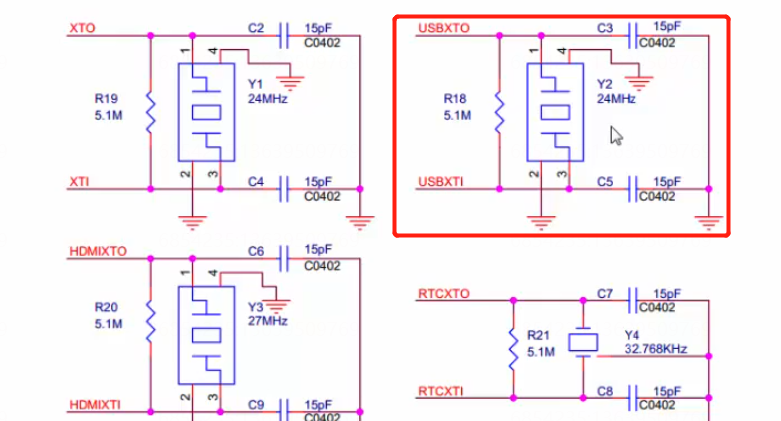

内部USBXTO进行了焊接

在芯片手册对应(P354)

XUSBXTI重点要看的

时钟来源:晶振+时钟发生器+PLL+分频电路

(1)S5PV210外部有4个晶振接口,设计板子硬件时可以根据需要来决定在哪里接晶振。接了晶振之后上电相应的模块就能产生振荡,产生原始时钟。原始时钟再经过一系列的筛选开关进入相应的PLL电路生成倍频后的高频时钟。高频时钟再经过分频到达芯片内部各模块上。(有些模块,譬如串口内部还有进一步的分频器进行再次分频使用)

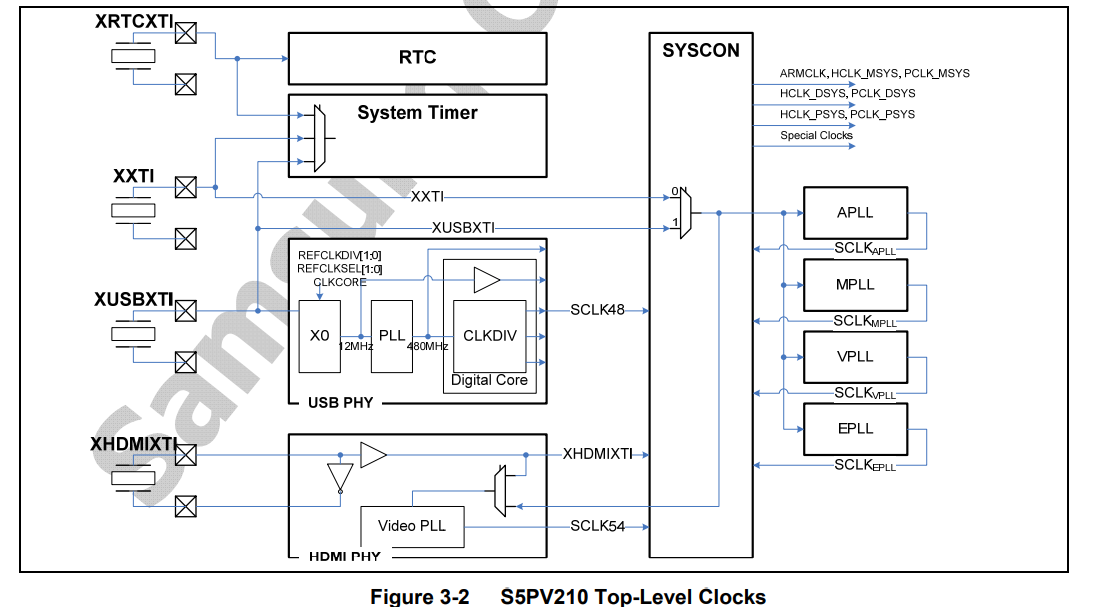

PLL:APLL、MPLL、EPLL、VPLL

APLL:Cortex-A8内核 MSYS域

MPLL&EPLL:DSYS PSYS

VPLL:Video视频相关模块

CLOCKS FROM CMU

CMU generates internal clocks with intermediate frequencies using clocks from the clock pads (that is, XRTCXTI,

XXTI, XUSBXTI, and XHDMIXTI), four PLLs (that is, APLL, MPLL, EPLL, and VPLL), USB PHY and HDMI PHY

clock. Some of these clocks can be selected, pre-scaled, and provided to the corresponding modules.

It is recommended to use 24MHz input clock source for APLL, MPLL, EPLL and VPLL.

To generate internal clocks, the following components are used.

• APLL uses FINPLL (refer to Figure 3-1) as input to generate 30MHz ~ 1GHz.

• MPLL uses FINPLL as input to generate 50MHz ~ 2GHz.

• EPLL uses FINPLL as input to generate 10MHz ~ 600MHz.

• VPLL uses FINPLL or SCLK_HDMI27M as input to generate 10MHz ~ 600MHz. This PLL generates 54MHz

video clock.

• USB OTG PHY uses XUSBXTI to generate 30MHz and 48MHz

• HDMI PHY uses XUSBXTI or XHDMIXTI to generate 54MHz

In typical S5PV210 applications,

• Cortex A8 and MSYS clock domain uses APLL (that is, ARMCLK, HCLK_MSYS, and PCLK_MSYS).

• DSYS and PSYS clock domain (that is, HCLK_DSYS, HCLK_PSYS, PCLK_DSYS, and PCLK_PSYS) and

other peripheral clocks (that is, audio IPs, SPI, and so on) use MPLL and EPLL.

• Video clocks uses VPLL.

Clock controller allows bypassing of PLLs for slow clock. It also connects/ disconnects the clock from each block (clock gating) using software, resulting in power reduction.

CLOCK RELATIONSHIP

Clocks have the following relationship:

• MSYS clock domain

− freq(ARMCLK) = freq(MOUT_MSYS) / n, where n = 1 ~ 8

− freq(HCLK_MSYS) = freq(ARMCLK) / n, where n = 1 ~ 8

− freq(PCLK_MSYS) = freq(HCLK_MSYS) / n, where n = 1 ~ 8

− freq(HCLK_IMEM) = freq(HCLK_MSYS) / 2

• DSYS clock domain

− freq(HCLK_DSYS) = freq(MOUT_DSYS) / n, where n = 1 ~ 16

− freq(PCLK_DSYS) = freq(HCLK_DSYS) / n, where n = 1 ~ 8

• PSYS clock domain

− freq(HCLK_PSYS) = freq(MOUT_PSYS) / n, where n = 1 ~ 16

− freq(PCLK_PSYS) = freq(HCLK_PSYS) / n, where n = 1 ~ 8

− freq(SCLK_ONENAND) = freq(HCLK_PSYS) / n, where n = 1 ~ 8

Values for the high-performance operation:

• freq(ARMCLK) = 1000 MHz

• freq(HCLK_MSYS) = 200 MHz

• freq(HCLK_IMEM) = 100 MHz

• freq(PCLK_MSYS) = 100 MHz

• freq(HCLK_DSYS) = 166 MHz

• freq(PCLK_DSYS) = 83 MHz

• freq(HCLK_PSYS) = 133 MHz

• freq(PCLK_PSYS) = 66 MHz

• freq(SCLK_ONENAND) = 133 MHz, 166 MHz

• PLL

− APLL can drive MSYS domain and DSYS domain. It can generate up to 1 GHz, 49:51 duty ratio.

− MPLL can drive MSYS domain and DSYS domain. It supplies clock, up to 2 GHz and 40:60 duty ratio.

− EPLL is mainly used to generate audio clock.

− VPLL is mainly used to generate video system operating clock, 54 MHz.

− Typically, APLL drives MSYS domain and MPLL drives DSYS domain.

NOTE: Although there is the equation for choosing PLL value, we strongly recommend only the values in the PLL value

recommendation table. If you have to use other values, please contact us.

MSYS域:

ARMCLK: 给cpu内核工作的时钟,也就是所谓的主频。

HCLK_MSYS: MSYS域的高频时钟,给DMC0和DMC1使用

PCLK_MSYS: MSYS域的低频时钟

HCLK_IMEM:给iROM和iRAM(合称iMEM)使用

其中最重要的是:ARMCLK、HCLK_MSYS

DSYS域:

HCLK_DSYS:DSYS域的高频时钟

PCLK_DSYS:DSYS域的低频时钟

PSYS域:

HCLK_PSYS:PSYS域的高频时钟

PCLK_PSYS:PSYS域的低频时钟

SCLK_ONENAND:

总结:

210内部的各个外设都是接在(内部AMBA总线)总线上面的,AMBA总线有1条高频分支叫AHB,有一条低频分支叫APB。上面的各个域都有各自对应的HCLK_XXX和PCLK_XXX,其中HCLK_XXX就是XXX这个域中AHB总线的工作频率;PCLK_XXX就是XXX这个域中APB总线的工作频率。

SoC内部的各个外设其实是挂在总线上工作的,也就是说这个外设的时钟来自于他挂在的总线,譬如串口UART挂在PSYS域下的APB总线上,因此串口的时钟来源是PCLK_PSYS。

我们可以通过记住和分析上面的这些时钟域和总线数值,来确定我们各个外设的具体时钟频率。

各时钟典型值(默认值,iROM中设置的值)

(1)当210刚上电时,默认是外部晶振+内部时钟发生器产生的24MHz频率的时钟直接给ARMCLK的,这时系统的主频就是24MHz,运行非常慢。

(2)iROM代码执行时第6步中初始化了时钟系统,这时给了系统一个默认推荐运行频率。这个时钟频率是三星推荐的210工作性能和稳定性最佳的频率。

(3)各时钟的典型值:

? freq(ARMCLK) = 1000 MHz

? freq(HCLK_MSYS) = 200 MHz

? freq(HCLK_IMEM) = 100 MHz

? freq(PCLK_MSYS) = 100 MHz

? freq(HCLK_DSYS) = 166 MHz

? freq(PCLK_DSYS) = 83 MHz

? freq(HCLK_PSYS) = 133 MHz

? freq(PCLK_PSYS) = 66 MHz

? freq(SCLK_ONENAND) = 133 MHz, 166 MHz